Science

Researchers Develop Novel Algorithm for IC Power Analysis Datasets

In a significant advancement for the field of integrated circuit (IC) design, a research team from the College of Information Science and Electronic Engineering at Zhejiang University and Shanghai Hexin Industrial Software Co., Ltd. has developed a novel algorithm aimed at generating pseudo-datasets for power analysis in digital circuits. Their study, titled “Algorithm and evaluation of generating pseudo-datasets for integrated circuit power analysis,” addresses the growing need for extensive datasets in an era increasingly defined by data-driven machine learning (ML) methods.

The research highlights a critical gap in the availability of standard datasets within the IC industry, which are often insufficient in both quantity and specificity. Existing datasets frequently pose challenges due to copyright and legal constraints, complicating access to large-scale industrial or competitive data. In response, the team has crafted an innovative approach that generates pseudo-circuit datasets through a unique algorithm based on graph topology.

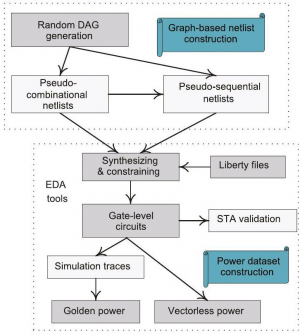

The algorithm operates by converting randomly generated directed acyclic graphs (DAGs) into gate-level Verilog pseudo-combinational circuit netlists. This method allows for the efficient creation of numerous examples for power analysis. Further enhancements involve the introduction of register units that transform these pseudo-combinational netlists into pseudo-sequential circuit netlists. Hyperparameters are employed to control circuit topology, while appropriate sequential constraints are integrated during synthesis, ultimately leading to the generation of a comprehensive pseudo-circuit dataset.

To assess the efficacy of their proposed methodology, the researchers utilized mainstream power analysis software, including Synopsys PrimeTime PX and Cadence Voltus. Pre-layout average power tests were conducted on the generated circuits, with results indicating that the pseudo-datasets—comprising 1,000 sets of combinational and 1,000 sets of sequential circuit netlists—demonstrated consistent power consumption distribution trends when compared to benchmark datasets.

The study not only confirms the effectiveness of the generated datasets but also showcases the operational efficiency and robustness of the algorithm. The results were validated through circuit topology complexity analysis and static timing analysis (STA), underscoring the research’s value in advancing IC power analysis methodologies.

Moreover, the algorithm’s design allows for the parallel generation of samples, significantly reducing time overhead. The sequential circuit generation factor, denoted as α, can also be adjusted to refine circuit topology and effectively address the zero-value phenomenon frequently encountered in sequential circuit power analysis.

The full text of the study, authored by Zejia LYU, Jizhong SHEN, and Xi CHEN, is available for further reading at https://doi.org/10.1631/FITEE.2400677. This research marks a vital step forward in enhancing data accessibility for integrated circuit power analysis, paving the way for more robust applications of machine learning in electronic design automation.

-

Lifestyle3 months ago

Lifestyle3 months agoLibraries Challenge Rising E-Book Costs Amid Growing Demand

-

Sports3 months ago

Sports3 months agoTyreek Hill Responds to Tua Tagovailoa’s Comments on Team Dynamics

-

Sports3 months ago

Sports3 months agoLiverpool Secures Agreement to Sign Young Striker Will Wright

-

Lifestyle3 months ago

Lifestyle3 months agoSave Your Split Tomatoes: Expert Tips for Gardeners

-

Lifestyle3 months ago

Lifestyle3 months agoPrincess Beatrice’s Daughter Athena Joins Siblings at London Parade

-

World3 months ago

World3 months agoWinter Storms Lash New South Wales with Snow, Flood Risks

-

Science3 months ago

Science3 months agoTrump Administration Moves to Repeal Key Climate Regulation

-

Business3 months ago

Business3 months agoSoFi Technologies Shares Slip 2% Following Insider Stock Sale

-

Science2 months ago

Science2 months agoSan Francisco Hosts Unique Contest to Identify “Performative Males”

-

Science3 months ago

Science3 months agoNew Tool Reveals Link Between Horse Coat Condition and Parasites

-

Sports3 months ago

Sports3 months agoElon Musk Sculpture Travels From Utah to Yosemite National Park

-

Science3 months ago

Science3 months agoNew Study Confirms Humans Transported Stonehenge Bluestones